#### **POLITECNICO** MILANO 1863 DIPARTIMENTO DI ELETTRONICA INFORMAZIONE E BIOINGEGNERIA

POLITECNICO MILANO 1863

# CopyCAN

An Error-Handling Protocol based Intrusion Detection System for Controller Area Network

Stefano Longari, Matteo Penco, Michele Carminati, Stefano Zanero Politecnico di Milano

11 Nov 2019 - ACM CPS-SPC

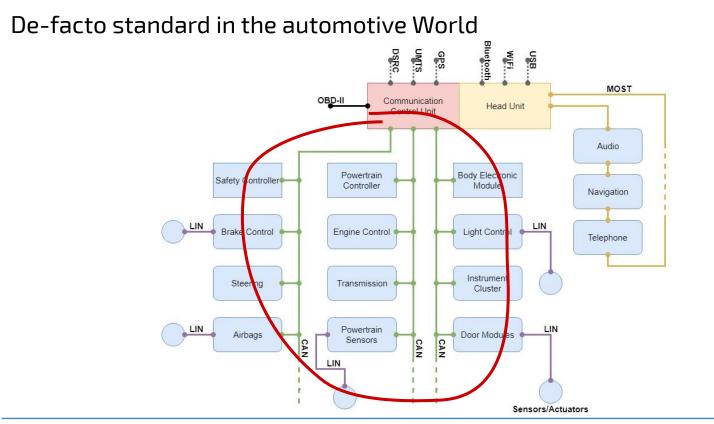

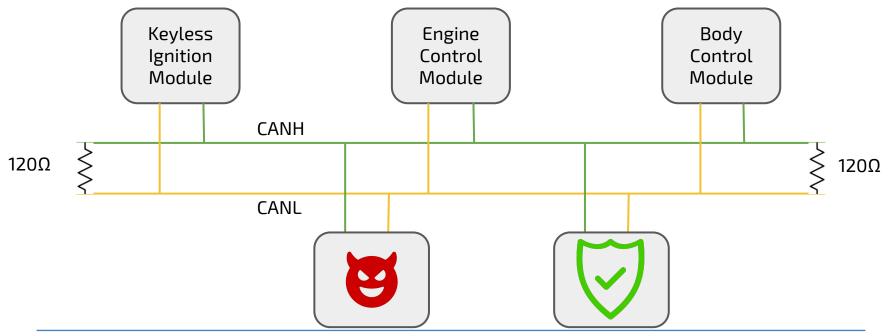

#### Controller Area Network

### Is CAN key to automotive attacks?

#### AUTO TECH Tesla hackers explain how they did it at Defcon

At the digital security conference, Kevin Mahaffey and Marc Rogers explain how they hacked a Tesla Model S -- and why you shouldn't be too alarmed.

BY ANTUAN GOODWIN 10 | AUGUST 9, 2015 2:09 PM PDT

Note: As stated below. Tesla has already patched many of the vulnerabilities discussed here in a recent patch.

LAS VEGAS -- It is very difficult to hack a Tesla Model S, but it's not impossible. Last week, researchers Kevin Mahaffey and Marc Rogers demonstrated that they were able to remotely unlock the Model S' doors, start the vehicle and drive away. They were also able to issue a

F 🗇 🖸

At Defcon, Rogers and Mahaffey (left to right) explain what Tesla does right and where it was weak in designing the Model S' information systems.

Antuan Goodwin/CNET

f 7 The Jeep Hackers Are Back to Prove Car Hacking Can Get Much Worse

#### ANDY GREENBERG SECURITY 08.01.16 03:30 PM

Security researchers Charlie Miller and Chris Valasek. 🙆 WHITNEY CURTIS FOR WIRED

#### What weaknesses are commonly abused?

#### Can we detect these attacks?

#### How do automotive IDS work?

Industrial secret, however we can make an educated guess at some methods

- Frequency based

- CAN messages are usually <u>periodic</u>

- Specification based

- Set rules for the <u>data</u> field of the message

- Potentially <u>dynamic</u> depending from message history

- Machine Learning based

- Generally similar to specification based ones

- o <u>Mainly Academic</u>

#### How to evade an automotive IDS

- Specification based: Comply with the rules

- Frequency based: Comply with the frequency

- ML based: different forms of mimicry attacks

#### The perfect crime

What if we manipulate/substitute a real frame?

- Specification based: Comply with the rules

- Frequency based: Comply with the frequency

- ML based: different forms of mimicry attacks

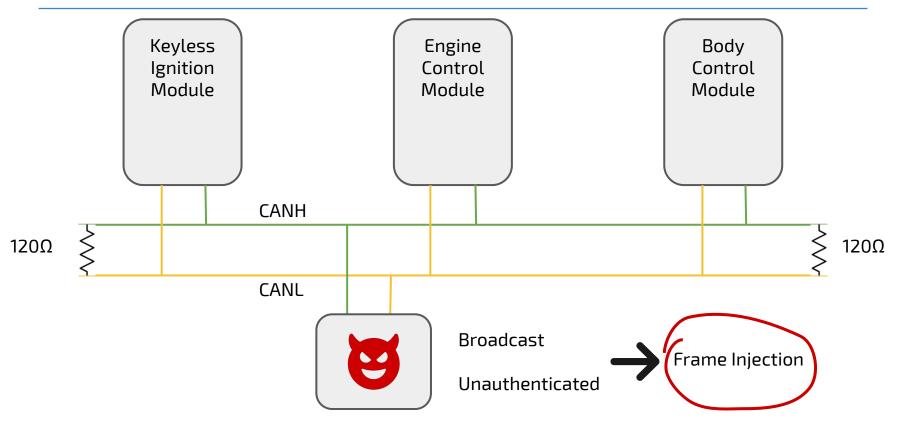

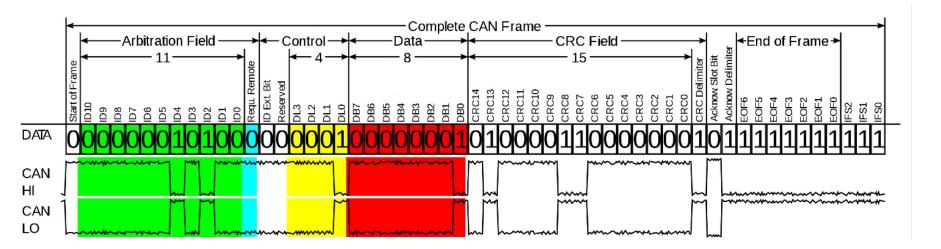

#### Data frames

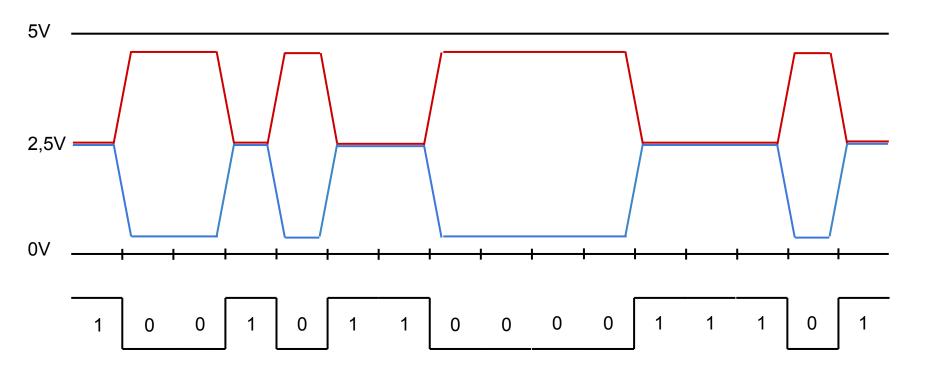

#### CAN bus values

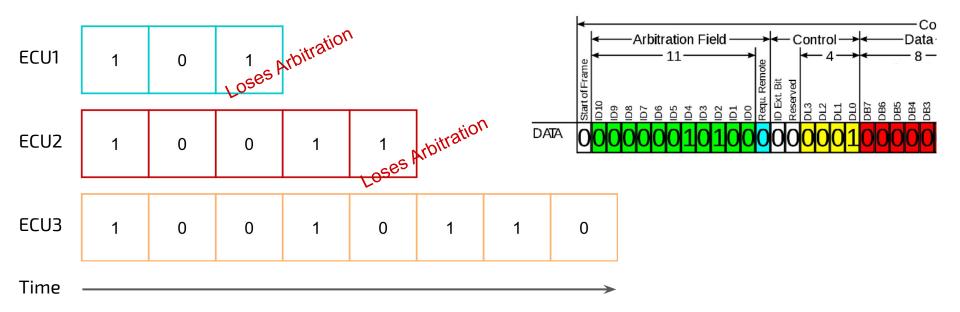

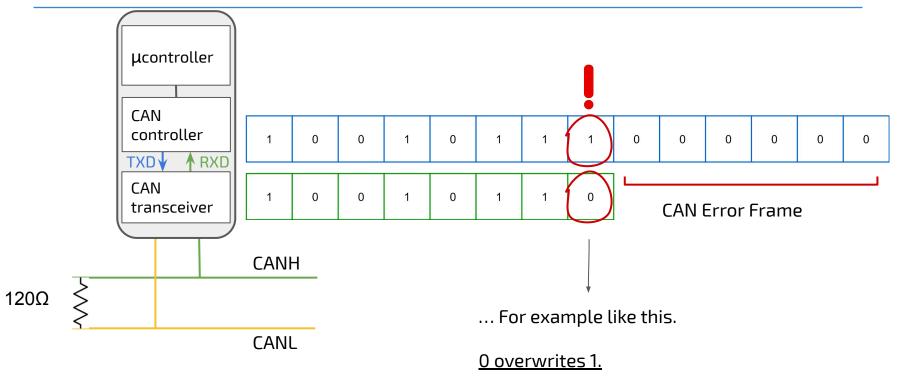

#### Dominant beats recessive - arbitration

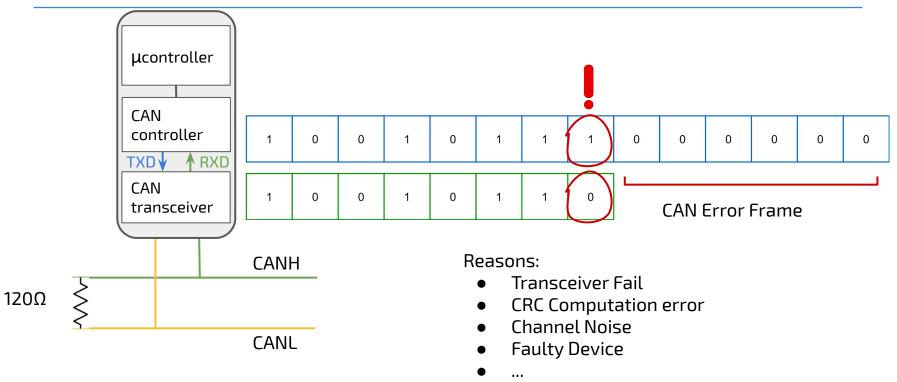

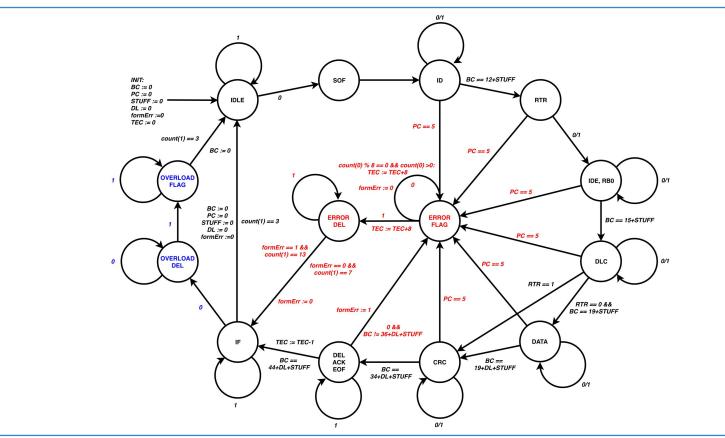

### CAN error handling

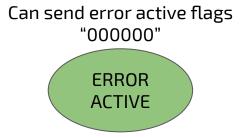

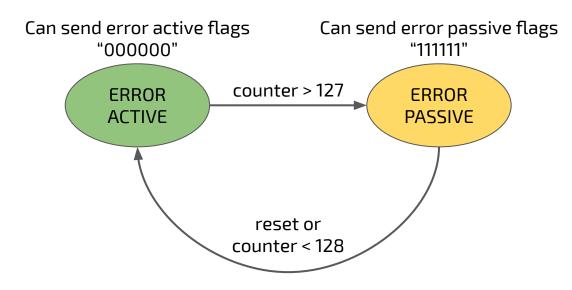

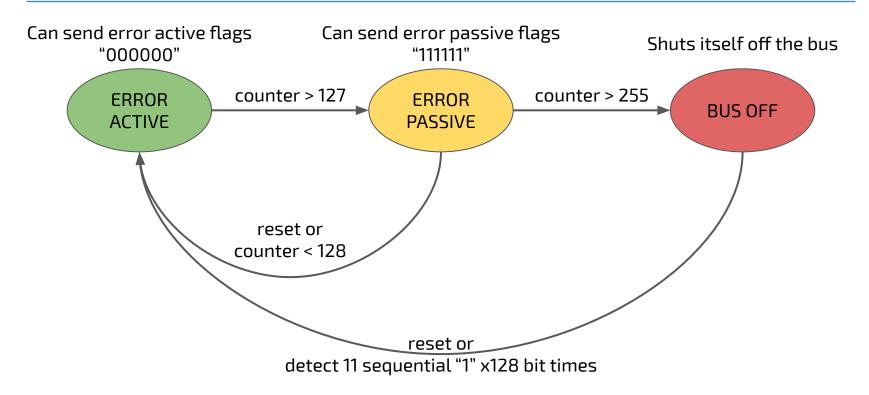

#### CAN fault confinement

### CAN fault confinement

## CAN fault confinement

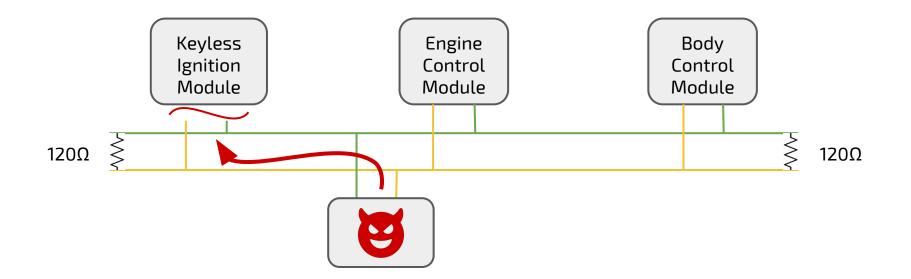

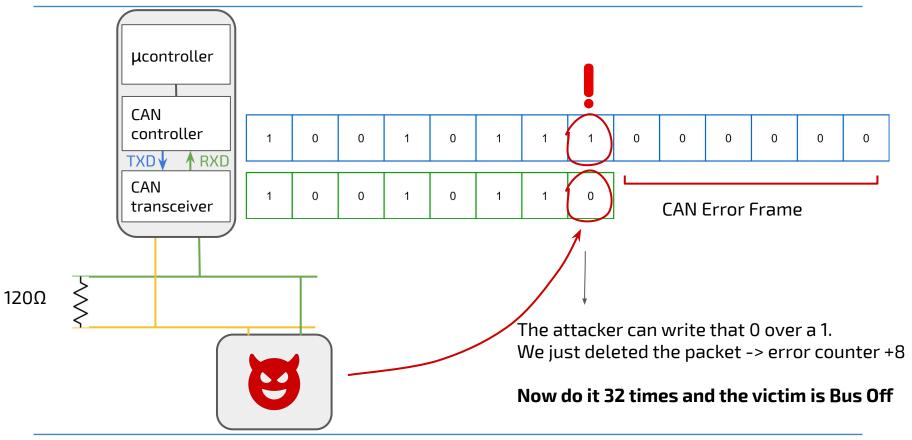

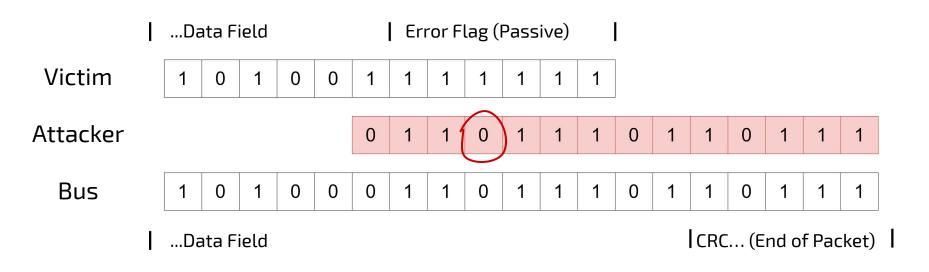

## How do we Exploit this?

How do we convince the target ECU to kick itself off the network?

#### How do we Exploit this?

### How do we Exploit this?

#### Attack scenarios

Denial of Service for the sake of Denial of Service

e.g. Ransomware

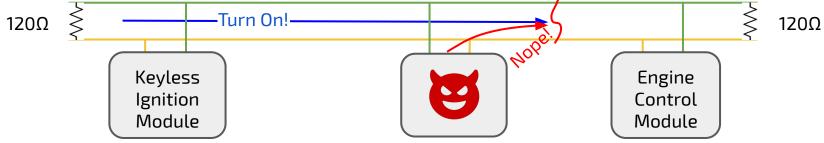

#### Attack scenarios

Detection avoidance for spoofing attacks

- Shut down the victim ECU

- Send spoofed data

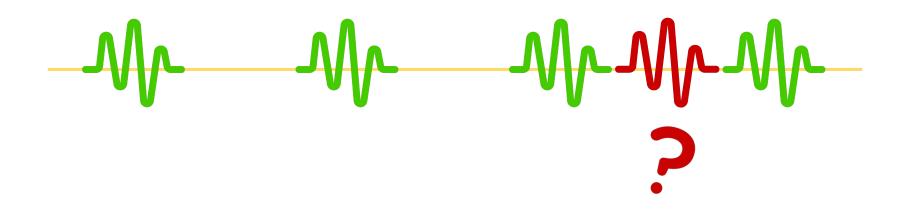

### Can we detect the DoS?

We can read data from the bus

We can detect the attacker once he tries to spoof data after the DoS

## We need to study more CAN specs! :(

#### List of rules that change the counters:

- 1. When a RECEIVER detects an error, the RECEIVE ERROR COUNT will be increased by 1, except when the detected error was a BIT ERROR during the sending of an ACTIVE ERROR FLAG or an OVERLOAD FLAG.

- 2. When a RECEIVER detects a 'dominant' bit as the first bit after sending an ERROR FLAG the RECEIVE ERROR COUNT will be increased by 8.

- 3. When a TRANSMITTER sends an ERROR FLAG the TRANSMIT ERROR COUNT is increased by 8.

#### Exception 1:

If the TRANSMITTER is 'error passive' and detects an ACKNOWLEDGMENT ERROR because of not detecting a 'dominant' ACK and does not detect a 'dominant' bit while sending its PASSIVE ERROR FLAG.

#### Exception 2:

If the TRANSMITTER sends an ERROR FLAG because a STUFF ERROR occurred during ARBITRATION, and should have been 'recessive', and has been sent as 'recessive' but monitored as 'dominant'.

In exceptions 1 and 2 the TRANSMIT ERROR COUNT is not changed.

- If an TRANSMITTER detects a BIT ERROR while sending an ACTIVE ERROR FLAG or an OVERLOAD FLAG the TRANSMIT ERROR COUNT is increased by 8.

- 5. If an RECEIVER detects a BIT ERROR while sending an ACTIVE ERROR FLAG or an OVERLOAD FLAG the RECEIVE ERROR COUNT is increased by 8.

- 6. Any node tolerates up to 7 consecutive 'dominant' bits after sending an ACTIVE ERROR FLAG, PASSIVE ERROR FLAG or OVERLOAD FLAG. After detecting the 14th consecutive 'dominant' bit (in case of an ACTIVE ERROR FLAG or an OVERLOAD FLAG) or after detecting the 8th consecutive 'dominant' bit following a PASSIVE ERROR FLAG, and after each sequence of additional eight consecutive 'dominant' bits every TRANSMITTER increases its TRANSMIT ERROR COUNT by 8 and every RECEIVER increases its RECEIVE ERROR COUNT by 8.

- After the successful transmission of a message (getting ACK and no error until END OF FRAME is finished) the TRANSMIT ERROR COUNT is decreased by 1 unless it was already 0.

- After the successful reception of a message (reception without error up to the ACK SLOT and the successful sending of the ACK bit), the RECEIVE ERROR COUNT is decreased by 1, if it was between 1 and 127. If the RECEIVE ERROR COUNT was 0, it stays 0, and if it was greater than 127, then it will be set to a value between 119 and 127.

- A node is 'error passive' when the TRANSMIT ERROR COUNT equals or exceeds 128, or when the RECEIVE ERROR COUNT equals or exceeds 128. An error condition letting a node become 'error passive' causes the node to send an ACTIVE ERROR FLAG.

- 10. A node is 'bus off' when the TRANSMIT ERROR COUNT is greater than or equal to 256.

- 11.An 'error passive' node becomes 'error active' again when both the TRANSMIT ERROR COUNT and the RECEIVE ERROR COUNT are less than or equal to 127.

- 12. An node which is 'bus off is permitted to become 'error active' (no longer 'bus off') with its error counters both set to 0 after 128 occurrence of 11 consecutive 'recessive' bits have been monitored on the bus.

### Not all of them...

#### List of rules that change the counters:

- When a RECEIVER detects an error, the RECEIVE ERROR COUNT will be increased by 1, except when the detected error was a BIT ERROR during the sending of an ACTIVE ERROR FLAG or an OVERLOAD FLAG.

- When a RECEIVER detects a 'dominant' bit as the first bit after sending an ERROR. FLAG the RECEIVE ERROR COUNT will be increased by 8.

- When a TRANSMITTER sends an ERROR FLAG the TRANSMIT ERROR COUNT is increased by 8.

#### Exception 1:

If the TRANSMITTER is 'error passive' and detects an ACKNOWLEDGMENT ERROR because of not detecting a 'dominant' ACK and does not detect a 'dominant' bit while sending its PASSIVE ERROR FLAG.

#### Exception 2:

If the TRANSMITTER sends an ERROR FLAG because a STUFF ERROR occurred during ARBITRATION, and should have been 'recessive', and has been sent as 'recessive' but monitored as 'dominant'.

In exceptions 1 and 2 the TRANSMIT ERROR COUNT is not changed.

. If an TRANSMITTER detects a BIT ERROR while sending an ACTIVE ERROR FLAG or an OVERLOAD FLAG the TRANSMIT ERROR COUNT is increased by 8.

5 If an RECEIVER detects a BIT ERROR while sending an ACTIVE ERROR FLAG or an OVERLOAD FLAG the RECEIVE ERROR COUNT is increased by 8.

- 6. Any node tolerates up to 7 consecutive 'dominant' bits after sending an ACTIVE ERROR FLAG, PASSIVE ERROR FLAG or OVERLOAD FLAG. After detecting the 14th consecutive 'dominant' bit (in case of an ACTIVE ERROR FLAG or an OVERLOAD FLAG) or after detecting the 8th consecutive 'dominant' bit following a PASSIVE ERROR FLAG, and after each sequence of additional eight consecutive 'dominant' bits every TRANSMITTER increases its TRANSMIT ERROR COUNT by 8 and every RECEIVER increases its RECEIVE ERROR COUNT by 8.

- After the successful transmission of a message (getting ACK and no error until END OF FRAME is finished) the TRANSMIT ERROR COUNT is decreased by 1 unless it was already 0.

- 8. After the successful reception of a message (reception without error up to the ACK SLOT and the successful sending of the ACK bit), the RECEIVE ERROR COUNT is decreased by 1, if it was between 1 and 127. If the RECEIVE ERROR COUNT was 0, it stays 0, and if it was greater than 127, then it will be set to a value between 119 and 127.

- 9. A node is 'error passive' when the TRANSMIT ERROR COUNT equals or exceeds 128, or when the RECEIVE ERROR COUNT equals or exceeds 128. An error condition letting a node become 'error passive' causes the node to send an ACTIVE ERROR FLAG.

- 10. A node is 'bus off' when the TRANSMIT ERROR COUNT is greater than or equal to 256.

- 11.An 'error passive' node becomes 'error active' again when both the TRANSMIT ERROR COUNT and the RECEIVE ERROR COUNT are less than or equal to 127.

- 12. An node which is 'bus off is permitted to become 'error active' (no longer 'bus off') with its error counters both set to 0 after 128 occurrence of 11 consecutive 'recessive' bits have been monitored on the bus.

## Modify the CAN Controller

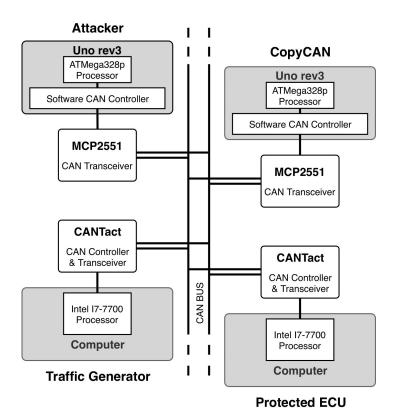

# Complete IDS process: CopyCAN

- 1) Define which ECUs/IDs to defend

- 2) Monitor the bus from the beginning of communication

- 3) Count the TEC (Transmit Error Counter) of each ECU

- 4) Detect when the ECU goes Bus Off

- 5) If the ECU writes on the bus again, flag as attack.

## Proof of Concept implementation:

Testbed to detect rules 4 and 6 "in the wild":

Tests done50Frames sent per test15000

**IDS Never failed**

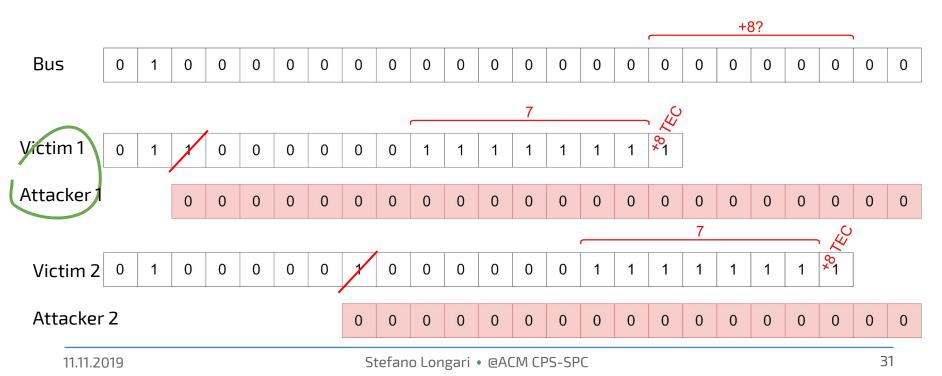

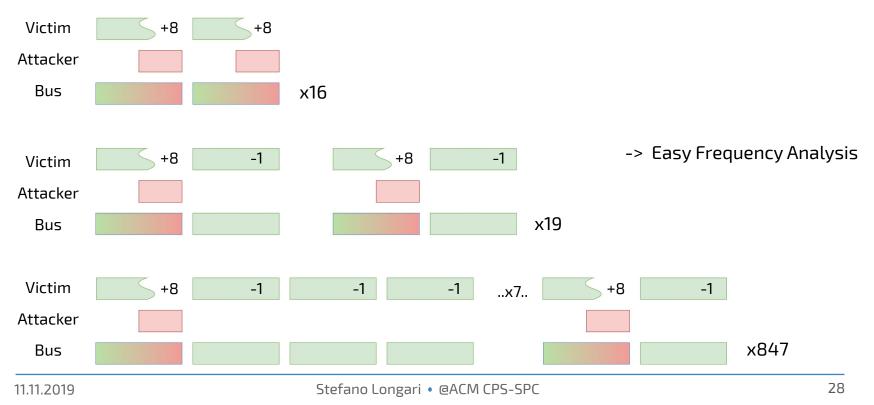

## Our Miscalculation (and solution)

## Our Miscalculation (and solution)

The attacker has to send a valid packet... But the victim wants to send it too!

#### Conclusions

DoS for CAN is not preventable...

... but the goals of the attacker may be!

# Thanks!

For any questions:

# Rule 6

Any node tolerates up to 7 consecutive 'dominant' bits after sending an ACTIVE ERROR FLAG, PASSIVE ERROR FLAG or OVERLOAD FLAG. After detecting the 14th consecutive 'dominant' bit (in case of an ACTIVE ERROR FLAG or an OVERLOAD FLAG) or after detecting the 8th consecutive 'dominant' bit following a PASSIVE ERROR FLAG, and after each sequence of additional 8 consecutive 'dominant' bits every TRANSMITTER increases its TRANSMIT ERROR COUNT by 8 and every RECEIVER increases its RECEIVE ERROR COUNT by 8.

# Rule 6

Cannot let the attacker <u>bypass</u> the whole IDS, so we always consider case 1